Решение системы уравнений в симулинке

Дифференциальные уравнения и системы уравнений

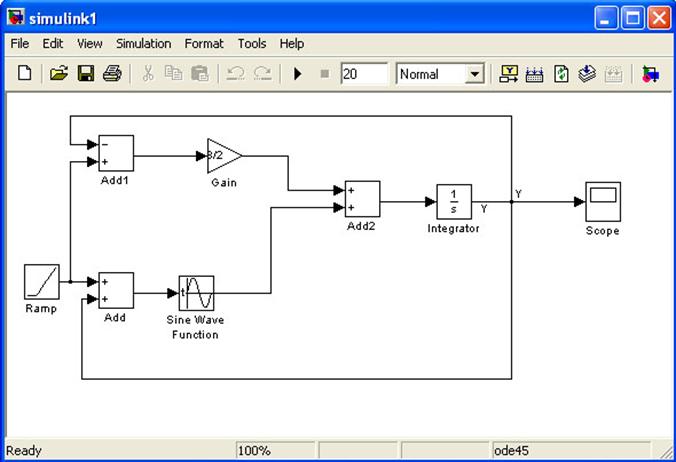

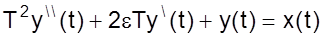

Необходимо решить уравнение:

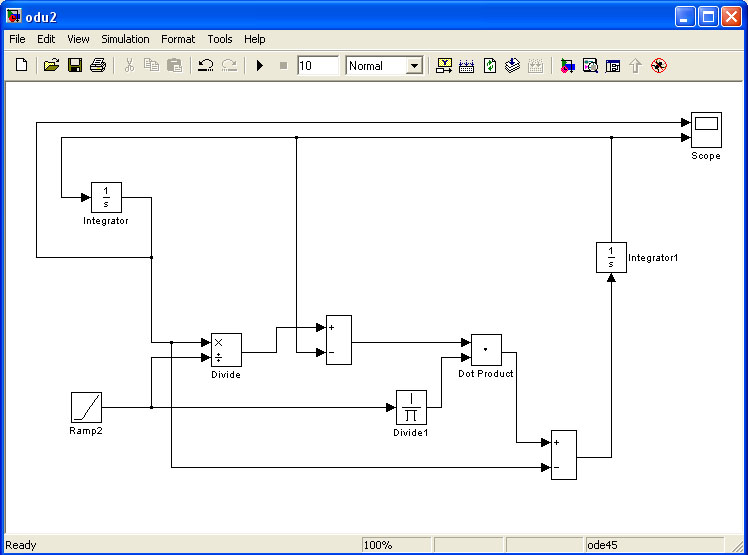

Попробуем решить его с помощью программы Simulink пакета MATLAB.

Метод решения дифференциальных уравнений отличается от традиционного. Нам необходимо создать схему уравнения. Необходимо будет создать обратную связь между выходными значениями интегратора и новым значением переменной. У нашего уравнения линейно изменяется x от 0 до 20. Поэтому для решения уравнения необходимо использовать блок Ramp . В конце обязательно должен быть интегрирующий блок, а из него результат выходит на осциллограф.

Решение уравнения выглядит так:

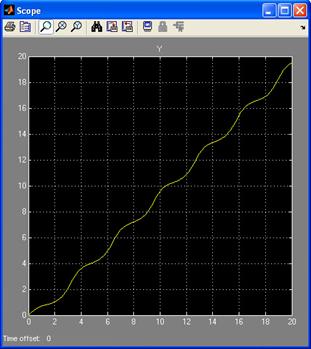

Результатом будет график x от y :

Рассмотрим из каких библиотек взяты использованные блоки.

Ramp – из Sources. Формирует линейный сигнал . В параметрах необходимо задать 1.

Add – Math Operations. В параметрах выбираем необходимые нам операции.

Gain – Math Operations . Коэффициент усиления сигнала. В параметрах ставим значение 3/2.

Sine Wave Function – Sources. Т.к. нам необходим косинус, то в параметрах Phase ставим pi/2.

Integrator – Continuous . Выполняет интегрирование входного сигнала.

Scope – Sinks . Выводим результат – график сигнала в функции времени.

Дифференциальные уравнения 2-го порядка.

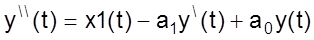

Дана система уравнений:

Решим ее с помощью программы Simulink пакета MATLAB.

Решаем аналогично предыдущему случаю.

В данной системе уравнений линейно изменяется x от 1 до 10. Также необходимо сделать обратную связь между выходными значениями интеграторов и новым значение переменной x . Обязательно надо в интеграторах задать начальные значения y1(0) = 0.1; y2(0) = 0.5.

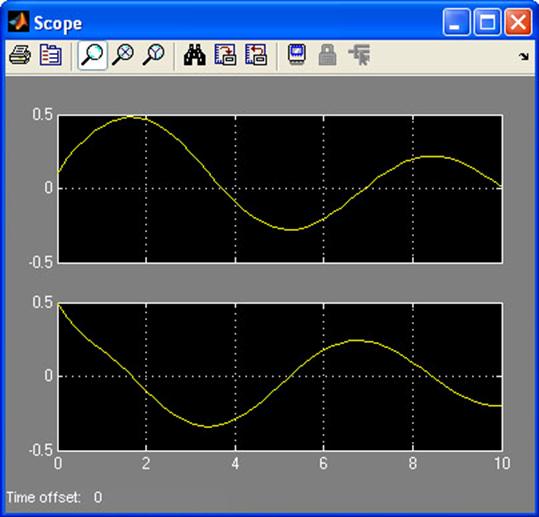

Результатом будут два графика:

Рассмотрим из каких библиотек взяты использованные блоки.

Ramp – из Sources . Формирует линейный сигнал. В параметрах необходимо задать все значения 1.

Integrator – Continuous . Выполняет интегрирование входного сигнала. Необходимо задать начальные значения Initial condition для y 1 0.1, для y 2 0.5.

Add – Math Operations . В параметрах выбираем необходимые нам операции.

Divide — Math Operations . Деление первой входной величины на вторую.

Dot Product — Math Operations. Перемножение .

Scope – Sinks. Выводим результат – график сигнала в функции времени.

Решение дифференциального уравнения различными методами, доступными SIMULINK

Страницы работы

Содержание работы

Файл Модели\САМРаботы02\САМ06а.doc 5 стр. 200 Кбайт

1. Решение дифференциального уравнения различными методами, доступными SIMULINK.

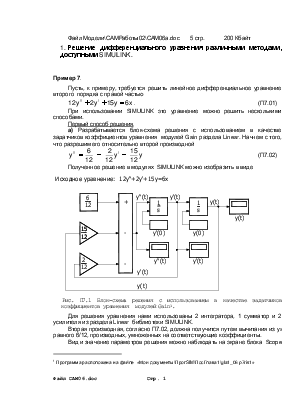

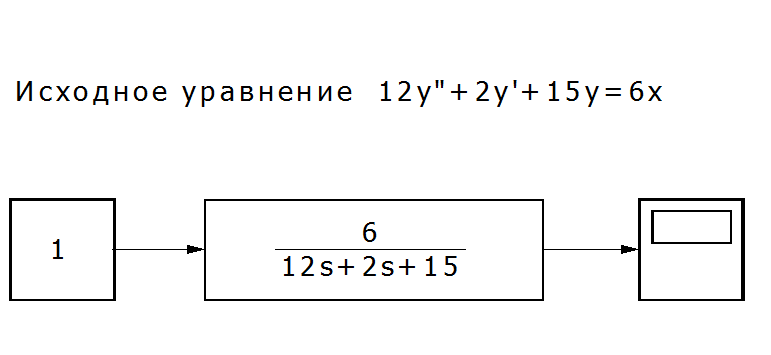

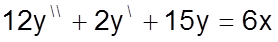

Пусть, к примеру, требуется решить линейное дифференциальное уравнение второго порядка с правой частью

При использовании SIMULINK это уравнение можно решить несколькими способами.

Первый способ решения.

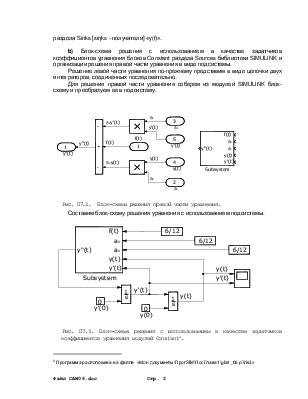

а) Разрабатывается блок-схема решения с использованием в качестве задатчиков коэффициентов уравнения модулей Gain раздела Linear. Начнем с того, что разрешим его относительно второй производной

Полученное решение в модулях SIMULINK можно изобразить в виде

Рис. П7.1 Блок-схема решения с использованием в качестве задатчиков коэффициентов уравнения модулей Gain[1].

Для решения уравнения нами использованы 2 интегратора, 1 сумматор и 2 усилителя из раздела Linear библиотеки SIMULINK.

Вторая производная, согласно П7.02, должна получится путем вычитания из y0 равного 6/12, производных, умноженных на соответствующие коэффициенты.

Вид и значение параметров решения можно наблюдать на экране блока Scope раздела Sinks [siŋks — получатели] «y(t)».

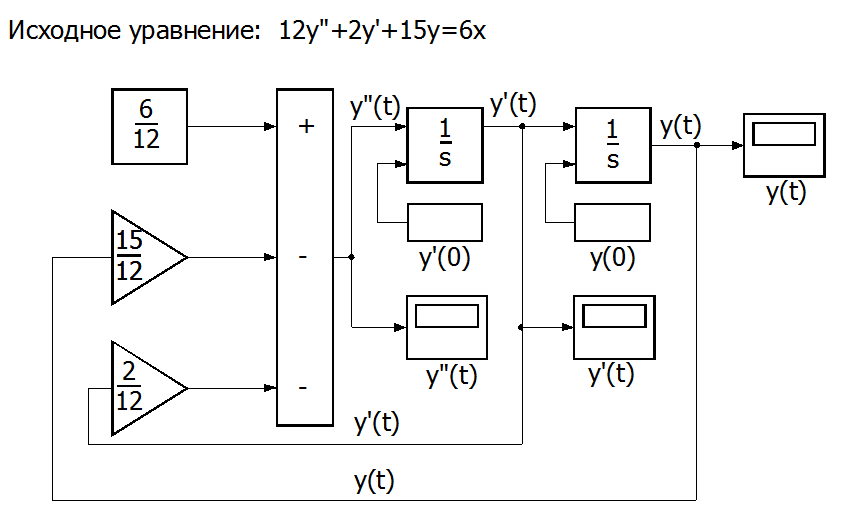

b) Блок-схема решения с использованием в качестве задатчиков коэффициентов уравнения блоков Constant раздела Sources библиотеки SIMULINK и организации решения правой части уравнения в виде подсистемы.

Решение левой части уравнения по-прежнему представим в виде цепочки двух интеграторов, соединенных последовательно.

Для решения правой части уравнения соберем из модулей SIMULINK блок-схему и преобразуем ее в подсистему.

Рис. П7.2. Блок-схема решения правой части уравнения.

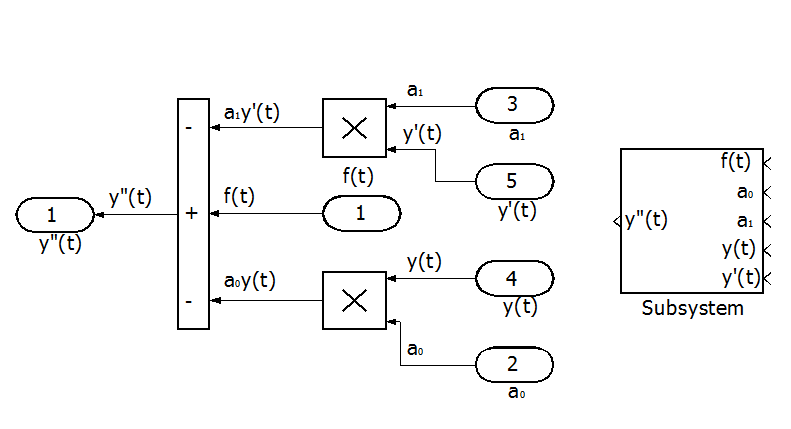

Составим блок-схему решения уравнения с использованием подсистемы.

Рис. П7.3. Блок-схема решения с использованием в качестве задатчиков коэффициентов уравнения модулей Constant[2].

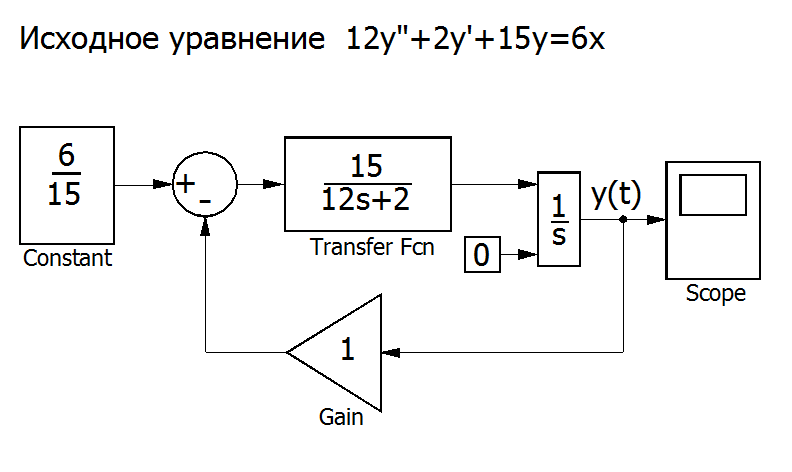

Второй способ решения.

Используя SIMULINK, можно представить другой способ решения этого уравнения. Решение можно получить, используя модуль Transfer Fcn [‘trænsfə: Fkn] (Передаточное звено). В качестве входного сигнала будем использовать блок Constant раздела Sources [so:s — источники]

Рис. П7.4. Решение уравнения с использованием типовых структурных схем[3].

Вид и значение параметров решения можно наблюдать на экране блока Scope раздела Sinks [siŋks — получатели] «Интеграл».

Третий способ решения.

SIMULINK может предложить еще один способ решения данного дифференциального уравнения. Воспользовавшись методами структурных преобразований, данное уравнение можно представить в виде структурной схемы, состоящей из типовых модулей.

Рис. П7.5. Решение уравнения с использованием структурных преобразований[4].

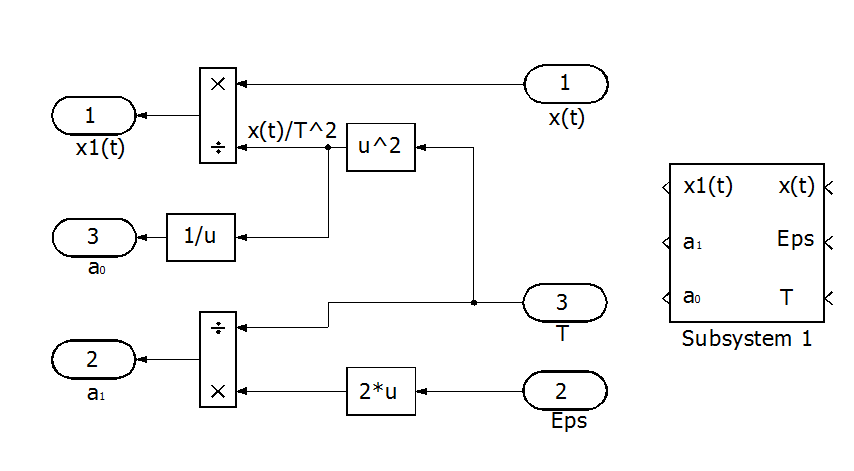

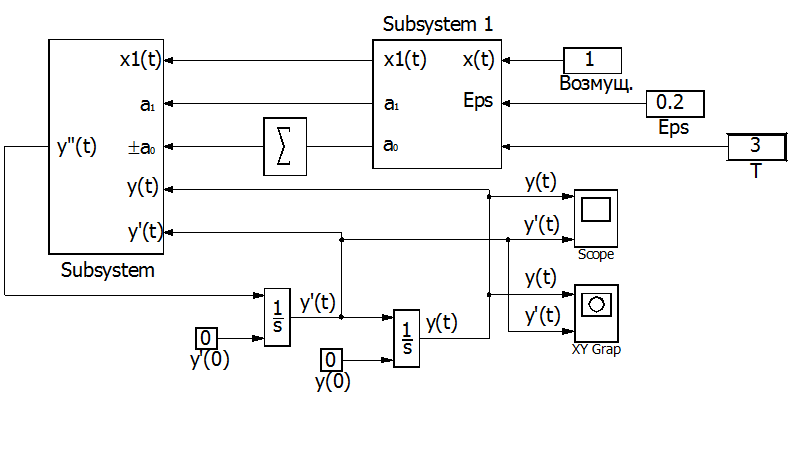

Проведем исследование дифференциального уравнения 2 порядка

методами фазовой плоскости, используя возможности SIMULINK.

Начнем с того, что разрешим уравнение относительно старшей производной.

Решение левой части уравнения представим в виде цепочки из двух интеграторов соответственно настроенных.

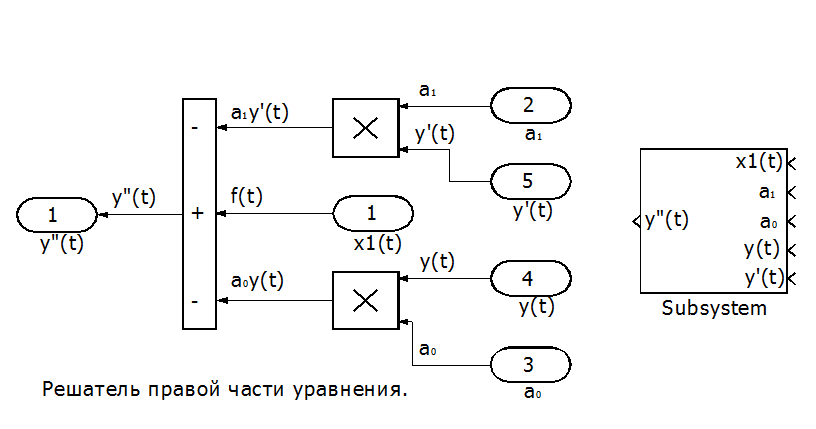

Для решения правой части уравнения создадим 2 подсистемы. Одну для формирования значений коэффициентов уравнения, разрешенного относительно старшей производной и вторую для решения собственно правой части уравнения.

Рис. П8.1 Блок-схема формирования коэффициентов уравнения.

Рис. П8.2. Решатель правой части уравнения.

Решение дифференциального уравнения с учетом созданных подсистем будет иметь вид

Рис. П8.3. Блок-схема решения дифференциального уравнения[5].

Исследование фазового портрета.

Для наблюдения за фазовыми траекториями включим в качестве смотрового окна в блок-схему решения уравнения рис. П7.3 дополнительно модуль XY Graph из раздела Sinks библиотеки SIMULINK.

Сущность метода фазовой плоскости заключается в построении фазовых траекторий по дифференциальным уравнениям в системе координат: ось x — значение исследуемой величины u, ось y – скорость ее изменения du/dt. Процесс изменения траектории представляет собой движение изображающей точки на фазовой плоскости. Начальные условия определяют первоначальное положение изображающей точки на фазовой плоскости. Совокупность фазовых траекторий в плоскости (x, y) носит название фазовый портрет. Подробнее с методами фазовой плоскости можно ознакомиться по «Иващенко Н.Н. Автоматическое регулирование. Теория и элементы систем. Учебник для вузов. Изд. 4-е, перераб. и доп. М., «Машиностроение», 1978. Стр. 485-495».

Задачей нашего исследования является построение некоторых наиболее характерных фазовых портретов.

Рассмотрим следующие случаи характерные для уравнения 2 порядка:

[1] Программа расположена на файле «Мои документы\ПрогSIM\ПосГлава1\gla1_06 p7ris1»

[2] Программа расположена на файле «Мои документы\ПрогSIM\ПосГлава1\gla1_06 p7ris3»

[3] Программа расположена на файле «Мои документы\ПрогSIM\ПосГлава1\gla1_06 p7ris4»

[4] Программа расположена на файле «Мои документы\ПрогSIM\ПосГлава1\gla1_06 p7ris5»

[5] Программа расположена на файле «Мои документы\ПрогSIM\ПосГлава1\gla1_06 p8ris3»

Решение системы уравнений в симулинке

И.В.Черных. «Simulink: Инструмент моделирования динамических систем»

9. Библиотека блоков Simulink

9.3. Continuous – аналоговые блоки

9.3.1. Блок вычисления производной Derivative

Выполняет численное дифференцирование входного сигнала.

Для вычисления производной используется приближенная формула Эйлера:

где

Значение входного сигнала блока до начала расчета считается равным нулю. Начальное значение выходного сигнала также полагается равным нулю.

Точность вычисления производной существенно зависит от величины установленного шага расчета. Выбор меньшего шага расчета улучшает точность вычисления производной.

На рис. 9.3.1 показан пример использования дифференцирующего блока для вычисления производной прямоугольного сигнала. В рассматриваемом примере, для повышения наглядности, шаг расчета выбран достаточно большим.

Рис.9.3.1. Использование блока Derivative для дифференцирования сигнала.

Данный блок используется для дифференцирования аналоговых сигналов. При дифференцировании дискретного сигнала с помощью блока Derivative его выходной сигнал будет представлять собой последовательность импульсов соответствующих моментам времени скачкообразного изменения дискретного сигнала.

9.3.2. Интегрирующий блок lntegrator

Выполняет интегрирование входного сигнала.

- none – нет (сброс не выполняется),

- rising — нарастающий сигнал (передний фронт сигнала),

- falling — спадающий сигнал (задний фронт сигнала),

- either – нарастающий либо спадающий сигнал,

- level – не нулевой сигнал (сброс выполняется если сигнал на управляющем входе становится не равным нулю);

В том случае, если выбран какой-либо (но не none), тип управляющего сигнала, то на изображении блока появляется дополнительный управляющий вход. Рядом с дополнительным входом будет показано условное обозначение управляющего сигнала.

- Initial condition source — Источник начального значения выходного сигнала. Выбирается из списка:

- internal – внутренний

- external – внешний. В этом случае на изображении блока появляется дополнительный вход, обозначенный x0, на который необходимо подать сигнал задающий начальное значение выходного сигнала интегратора.

- Initial condition — Начальное условие. Установка начального значения выходного сигнала интегратора. Параметр доступен, если выбран внутренний источник начального значения выходного сигнала.

- Limit output (флажок) — Использование ограничения выходного сигнала.

- Upper saturation limit — Верхний уровень ограничения выходного сигнала. Может быть задан как числом, так и символьной последовательностью inf, то есть +

- Lower saturation limit — Нижний уровень ограничения выходного сигнала. Может быть задан как числом, так и символьной последовательностью inf, то есть —

- Show saturation port — управляет отображением порта, выводящего сигнал, свидетельствующий о выходе интегратора на ограничение. Выходной сигнал данного порта может принимать следующие значения:

- Ноль , если интегратор не находится на ограничении.

- +1 , если выходной сигнал интегратора достиг верхнего ограничивающего предела.

- -1 , если выходной сигнал интегратора достиг нижнего ограничивающего предела.

- Show state port (флажок) — Отобразить/скрыть порт состояния блока. Данный порт используется в том случае, если выходной сигнал интегратора требуется подать в качестве сигнала обратной связи этого же интегратора. На пример, при установке начальных условий через внешний порт или при сбросе интегратора через порт сброса. Выходной сигнал с этого порта может использоваться также для организации взаимодействия с управляемой подсистемой.

- Absolute tolerance — Абсолютная погрешность.

На рис. 9.3.2 показан пример работы интегратора при подаче на его вход ступенчатого сигнала. Начальное условие принято равным нулю.

Рис. 9.3.2. Интегрирование ступенчатого сигнала.

Пример на рис. 9.3.3 отличается от предыдущего подачей начального значения через внешний порт. Начальное значение выходного сигнала в данном примере задано равным –10.

Рис. 9.3.3. Интегрирование ступенчатого сигнала с установкой начального значения выходного сигнала.

Пример на рис. 9.3.4 демонстрирует использование входного порта для сброса выходного сигнала и порта состояния интегратора с целью организации обратной связи. Схема работает следующим образом: входной постоянный сигнал преобразуется интегратором в линейно-изменяющийся, по достижении выходным сигналом значения равного 1 блок Relational Operator вырабатывает логический сигнал, по переднему фронту которого происходит сброс выходного сигнала интегратора до начального значения равного нулю. В результате на выходе интегратора формируется пилообразный сигнал, изменяющийся от 0 до +1.

Рис. 9.3.4. Генератор пилообразного сигнала на основе интегратора.

Следующая схема (рис. 9.3.5) использует установку начального значения интегратора с помощью его выходного сигнала. В первый момент времени начальное значение выходного сигнала интегратора с помощью блока IC (Initial Condition) устанавливается равным нулю. По достижении выходным сигналом значения равного 1 блок Relational Operator подает сигнал сброса выходного сигнала интегратора на начальный уровень, при этом сигналом, задающим начальный уровень, оказывается инвертированный выходной сигнал интегратора (т.е. -1). Далее цикл работы схемы повторяется. В отличие от предыдущей схемы выходным сигналом генератора является двуполярный сигнал.

Рис. 9.3.5. Генератор двуполярного пилообразного сигнала

на основе интегратора.

Выполняет задержку входного сигнала на один временной такт.

На рис. 9.3.6 показан пример использования блока Memory для задержки дискретного сигнала на один временной такт.

Рис. 9.3.6. Применение блока для задержки сигнала на один временной такт

9.3.4. Блок фиксированной задержки сигнала Transport Delay

Обеспечивает задержку входного сигнала на заданное время.

Параметры:

При выполнении моделирования значение сигнала и соответствующее ему модельное время сохраняются во внутреннем буфере блока Transport Delay. По истечении времени задержки значение сигнала, извлекается из буфера и передается на выход блока. В том случае, если шаги модельного времени не совпадают со значениями моментов времени для записанного в буфер сигнала, блок Transport Delay выполняет аппроксимацию выходного сигнала.

В том случае, если начального значения объема памяти буфера не хватит для хранения задержанного сигнала, Simulink автоматически выделит дополнительную память. После завершения моделирования в командном окне MATLAB появится сообщение с указанием нужного размера буфера.

На рис. 9.3.7 показан пример использования блока Transport Delay для задержки прямоугольного сигнала на 0.5 с.

Рис. 9.3.7. Пример использования блока Transport Delay для задержки сигнала.

9.3.5. Блок управляемой задержки сигнала Variable Transport Delay

Выполняет задержку входного сигнала, заданную величиной сигнала управления.

Параметры:

Блок управляемой задержки Variable Transport Delay работает аналогично блоку постоянной задержки сигнала Transport Delay.

В том случае, если значение управляющего сигнала задающего величину задержки превышает значение, заданное параметром Maximum delay, то задержка выполняется на величину Maximum delay.

На рис. 9.3.8 показан пример использования блока Variable Transport Delay. Величина времени задержки сигнала изменяется от 0.5c до 1с в момент времени равный 5с.

Рис. 9.3.8. Пример использования блока Variable Transport Delay.

9.3.6. Блок передаточной функции Transfer Fcn

Блок передаточной характеристики Transfer Fcn задает передаточную функцию в виде отношения полиномов:

nn и nd – порядок числителя и знаменателя передаточной функции,

num – вектор или матрица коэффициентов числителя,

den – вектор коэффициентов знаменателя.

Параметры:

Порядок числителя не должен превышать порядок знаменателя.

Входной сигнал блока должен быть скалярным. В том случае, если коэффициенты числителя заданы вектором, то выходной сигнал блока будет также скалярным (как и входной сигнал). На рис. 9.3.8 показан пример моделирования колебательного звена с помощью блока Transfer Fcn.

Рис. 9.3.8. Пример моделирования колебательного звена.

Если коэффициенты числителя заданы матрицей, то блок Transfer Fcn моделирует векторную передаточную функцию, которую можно интерпретировать как несколько передаточных функций имеющих одинаковые полиномы знаменателя, но разные полиномы числителя. При этом выходной сигнал блока является векторным и количество строк матрицы числителя задает размерность выходного сигнала.

На рис. 9.3.9 показан пример блока Transfer Fcn задающий векторную передаточную функцию. Там же показана модель полностью аналогичная рассматриваемой по своим свойствам, но состоящая из отдельных блоков Transfer Fcn.

Рис. 9.3.9. Пример моделирования векторной передаточной функции и ее аналог.

Начальные условия при использовании блока Transfer Fcn полагаются нулевыми. Если же требуется, чтобы начальные условия не были нулевыми, то необходимо с помощью функции tf2ss (инструмент Control System Toolbox) перейти от передаточной функции к модели в пространстве состояний и моделировать динамический объект с помощью блока State-Space.

9.3.7. Блок передаточной функции Zero-Pole

Блок Zero-Pole определяет передаточную функцию с заданными полюсами и нулями:

Z – вектор или матрица нулей передаточной функции (корней полинома числителя),

P – вектор полюсов передаточной функции (корней полинома знаменателя),

K – коэффициент передаточной функции, или вектор коэффициентов, если нули передаточной функции заданы матрицей. При этом размерность вектора K определяется числом строк матрицы нулей.

Параметры:

Количество нулей не должно превышать число полюсов передаточной функции.

В том случае, если нули передаточной функции заданы матрицей, то блок Zero-Pole моделирует векторную передаточную функцию.

Нули или полюса могут быть заданы комплексными числами. В этом случае нули или полюса должны быть заданы комплексно-сопряженными парами полюсов или нулей, соответственно.

Начальные условия при использовании блока Zero-Pole полагаются нулевыми.

На рис. 9.3.10 показан пример использования блока Zero-Pole. В примере передаточная функция имеет один действительный нуль и два комплексно-сопряженных полюса.

Рис. 9.3.10. Пример использования блока Zero-Pole.

9.3.8. Блок модели динамического объекта State-Space

Блок создает динамический объект, описываемый уравнениями в пространстве состояний:

x – вектор состояния,

u – вектор входных воздействий,

y – вектор выходных сигналов,

A, B, C, D — матрицы: системы, входа, выхода и обхода, соответственно.

Размерность матриц показана на рис. 9.3.11 (n – количество переменных состояния, m – число входных сигналов, r – число выходных сигналов).

Рис. 9.3.11. Размерность матриц блока State-Space

Параметры:

- A –Матрица системы.

- B – Матрица входа.

- C – Матрица выхода

- D – Матрица обхода

- Initial condition – Вектор начальных условий.

- Absolute tolerance — Абсолютная погрешность.

На рис. 9.3.11 показан пример моделирования динамического объекта с помощью блока State-Space. Матрицы блока имеют следующие значения:

Рис. 9.3.12. Пример использования блока State-Space.

http://vunivere.ru/work13449

http://lokan.narod.ru/9_3.asp.htm